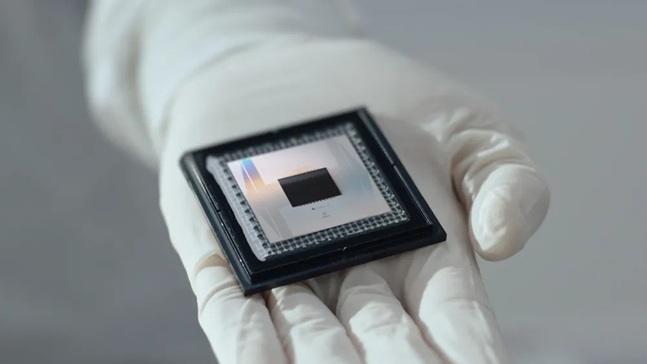

Chipmaker STMicroelectronics upped its game in Europe with plans to establish a pilot production line for next-generation Panel-Level Packaging (PLP) technology in France by Q3 2026.

It plans to test PLP production in a facility in the city of Tours as part of a broader $60 million investment to reshape its manufacturing footprint in France and Italy.

The company stated it is becoming harder for wafer-level packaging and flip-chip technology to connect silicon to external circuits as devices get smaller, requiring change in the techniques used.

STMicroelectronics explained PLP packs multiple ICs “on a single, larger rectangular substrate panel, rather than on individual circular wafers”, meaning more circuits can be processed at the same time, “reducing costs and improving throughput”.

Subscribe to our newsletter

Get breaking news, exclusive insight, and expert analysis - before anyone else.

President of quality, manufacturing and technology Fabio Gualandris said the technique could be used for RF, analogue, power and microcontrollers.

The pilot will span multiple teams and forms “a key part of a larger strategic initiative focused on heterogeneous integration”, Gualandris said.

STMicroelectronics operates a PLP production line in Malaysia.

Production on the “highly automated line” stands at more than 5 million units per day on panels measuring 700mm by 700mm.

Subscribe to our newsletter

Get breaking news, exclusive insight, and expert analysis - before anyone else.

Comments